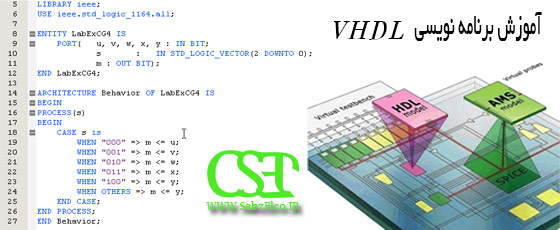

انواع آرایه ای یک یا چند عنصر از یک نوع را با هم و به صورت یک تک شیء گروه بندی می کنند. به هر عنصر آرایه می توان یک یا چند شاخص آرایه دسترسی داشت.

عناصر می توانند یکی از انواع VHDL باشند. برای نمونه، یک آرایه می تواند آرایه ها یا رکوردها را به عنوان عناصر خود داشته باشد.

در یک آرایه، تمام عناصر از یک نوع می باشند، مثال زیر یک اعلان نوع برای آرایه ای تک بعدی از بیت ها را نشان می دهد:

TYPE data_bus IS ARRAY(0 TO 31) OF BIT;

این اعلان یک نوع داده با نام data_bus اعلان می کند که آرایه ای 32 بیتی است. تمام عناصر آرایه شبیه به هم می باشند. با استاده از یک شاخص آرایه می توان به عناصر آرایه دسترسی پیدا کرد. نحوه دسترسی به عناصر آرایه در مثال زیر نشان داده شده است:

VARIABLE X : data_bus; VARIABLE Y : BIT; Y := X(0); --line 1 Y := X(15); --line 2

این مثال یک قطعه کد VHDL را نشان می دهد نه یک مدل کامل را. در خط 1، به نخستین عنصر آرایه X دسترسی می شود و به متغیر Y تخصیص می یابد که از نوع بیت است.

نوع Y بایستی با نوع مبنای آرایه X یکی باشد تا تخصیص انجام شود. اگر نوع ها یکسان نباشد، کامپایلر یک خطا تولید می کند.

در خط 2، شانزدهمین آرایه X دستیابی می شود زیرا شاخص آرایه از 0 شروع می شود. عنصر 0 نخستین عنصر است، عنصر 1 دومین عنصر و به همین ترتیب.

در زیر مثال جامع تری از دستیابی به آرایه ارائه می کنیم:

PACKAGE array_example IS

TYPE data_bus IS ARRAY(0 TO 31) OF BIT;

TYPE small_bus IS ARRAY(0 TO 7) OF BIT;

END array_example;

USE WORK.array_example.ALL;

ENTITY extract IS

PORT (data : IN data_bus;

Start : IN INTEGER;

data_out : OUT small_bus);

END extract;

ARCHITETURE test OF extract IS

BEGIN

PROCESS(data , start)

BEGIN

FOR i IN 0 TO 7 LOOP

data_out(i) <= data(i + start);

END LOOP;

END PROCESS;

END test;

این موجودیت یک عنصر آرایه 32 بیتی را به عنوان یک درگاه می گیرد و 8 بیت از عنصر را برمی گرداند. 8بیت برگشتی به مقدار شاخص start بستگی دارد. 8 بیت از طریق درگاه خروجی data_out برگردانده می شود.

تغییر در مقدار start یا data پروسس را برای اجرا تریگر می کند. حلقه FOR 8 بار تکرار می شود و هر بار یک تک بیت از درگاه data را به درگاه data_out کپی می کند.

نقطه شروع کپی در مقدار صحیح درگاه start رخ می دهد.هر بار در حلقه، به عنصر i ام data_out عنصر (i+start) ام داده تخصیص می یابد.

مثال های بالا آرایه ساده ای با انواع مبنای اسکالر داشته اند. در مثال زیر نوع مبنای آرایه، آرایه ای دیگر است:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

PACKAGE memory IS

CONSTANT width : INTEGER := 3;

CONSTANT memsize : INTEGER := 7;

TYPE data_out IS ARRAY(0 TO width) OF std_logic;

TYPE mem_data IS ARRAY(0 TO memsize) OF data_out;

END memory;

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE WORK.memory.ALL;

ENTTY rom IS

PORT( addr : IN INTEGER;

Data : OUT data_out;

Cs : IN std_logic);

END rom;

ARCHITECTURE basic OF rom IS

CONSTANT z_state : data_out := (‘Z’ , ‘Z’ , ‘Z’ , ‘Z’);

CONSTANT x_state : data_out := (‘X’ , ‘X’ , ‘X’ , ‘X’);

CONSTANT rom_data : mem_data :=

( (‘0’ , ‘0’ , ‘0’ , ‘0’),

(‘0’ , ‘0’ , ‘0’ , ‘1’),

(‘0’ , ‘0’ , ‘1’ , ‘0’),

(‘0’ , ‘0’ , ‘1’ , ‘1’),

(‘0’ , ‘1’ , ‘0’ , ‘0’),

(‘0’ , ‘1’ , ‘0’ , ‘1’),

(‘0’ , ‘1’ , ‘1’ , ‘0’),

(‘0’ , ‘1’ , ‘1’ , ‘1’) );

BEGIN

ASSERT addr <= memsize

REPORT “addr out of range”

SEVERITY ERROR;

Data <= rom_data(addr) AFTER 10 ns WHEN cs = ‘1’ ELSE

Z_state AFTER 20 ns WHEN cs = ‘0’ ELSE

X_state AFTER 10 ns;

END basic;

بسته حافظه برای تعریف دو نوع داده ای که ساختارهای داده موجودیت rom را می سازند از دو ثابت استفاده می کند. با تغییر پهنای باند ثابت و کامپایل دوباره، می توان پهنای خروجی حافظه را تغییر داد. داده های اولیه ROM را نیز می توان برای انعکاس پهنای جدید تغییر داد.

انواع داده بسته حافظه برای تعریف انواع داده درگاه های موجودیت نیز استفاده می شوند. به خصوص، درگاه داده از نوع data_out تعریف می شود.

این آموزش بیش از ۳ سال قبل ارسال شده و اکنون در لیست بهروزرسانیهای سایت قرار دارد. اگر پیشنهاد یا انتقادی برای بهبود آموزش دارید، خوشحال میشیم به ما اطلاع بدهید.

شما فارسی ای که در متن هاتون استفاده میکنید چرا اینقدر سنگین و قلمبه سلمبه است؟!! توضیحات کدهاتون انگار به زبان پشتو نوشته شده!! ممنون از کدهاتون ولی توضیحاتتون یک ریال هم نمی ارزه. ببخخشید البته

با سلام

دیدگاه هر شخص از مقاله منتشر شده می تواند متفاوت باشد.

هر جای مقاله منتشر شده را متوجه نشدید می توانید سوال کنید تا بیشتر توضیح دهم.

ممنون از نظرتون