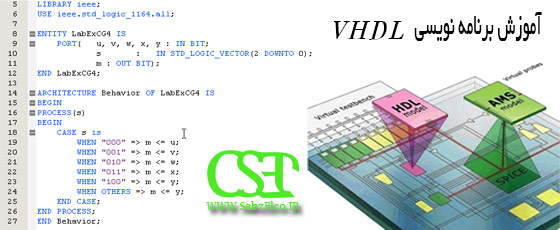

در VHDL هر شیء می تواند یکی از انواع سیگنال، متغییر و ثابت باشد.

سیگنال، سیم های اتصالی را نشان می دهد که درگاه های نمونه های قطعه را به هم متصل می کند.

متغییر، برای ذخیره محلی داده های موقتی استفاده می شود و فقط درون پروسس قابل رویت است.

ثابت، مقداری با نام مشخص است.

که در این بخش به بررسی سیگنال می پردازیم.

در ساخت مدل ها، از سیگنال ها برای اتصال موجودیت ها به یکدیگر استفاده می شود. سیگنال ها وسیله ای برای تبادل داده های پویا بین موجودیت ها می باشند.

اعلان یک سیگنال به صورت زیر است:

SIGNAL signal_name : signal_type [:= initial_value]

پس از کلید واژه SIGNAL یک یا چند نام سیگنال می آید. هر نام یک سیگنال جدید ایجاد می کند. نام سیگنال با یک دو نقطه (:) از نوع سیگنال جدا می شود.

نوع سیگنال، نوع داده اطلاعات سیگنال را مشخص می کند. همچنین سیگنال می تواند یک تصریح کننده مقدار اولیه داشته باشد تا بتوان سیگنال را مقدار دهی اولیه کرد.

سیگنال ها را می توان در بخش های اعلان موجودیت، معماری و بسته اعلان کرد. سیگنال هایی که در اعلان های بسته اعلان می شوند سیگنال های سراسری نیز نامیده می شوند زیرا در تمام موجودیت مشترک می باشند.

در زیر مثالی از اعلان های سیگنال آورده شده است:

LiBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

PACKAGE sigdecl IS

TYPE bus_type IS ARRAY(0 to 7) OF std_logic;

SIGNAL vcc : std_logic := ‘1’;

SIGNAL ground : std_logic := ‘0’;

FUNCTION magic_function ( a : IN bus_type) RETURN

Bus_type;

END sigdecl;

USE WORK.sigdecl.ALL;

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY board_design is

PORT( data_in : IN bus_type;

Data_out : OUT bus_type);

SIGNAL sys_clk : std_logic := ‘1’;

END board_design;

ARCHITECTURE data_flow OF board_design IS

SIGNAL int_bus : bus_type;

CONSTANT disconnect_value : bus_type := (‘X’, ‘X’, ‘X’, ‘X’, ‘X’, ‘X’, ‘X’, ‘X’);

BEGIN

Int_bus <= data_in WHEN sys_clk = ‘1’;

ELSE int_bus;

Data_out <= magic_function (int_bus) WHEN sys_clk = ‘0’

ELSE disconnect_value;

Sys_clk <= NOT(sys_clk) after 50 ns;

END data_flow;

سیگنال های vcc و ground در بسته sigdecl اعلان می شوند. چون این سیگنال ها در بسته اعلان می شوند می توانند توسط چند موجودیت استفاده شوند و بنابراین سیگنال های سراسری می باشند. برای استفاده از این سیگنال ها، هر موجودیت باید از بسته sigdecl استفاده کند. برای استفاده از بسته به یک بخش USE مانند زیر نیاز است:

USE work.sigdecl.vcc; USE work.sigdecl.ground;

یا:

USE work.sigdecl.ALL;

در مثال نخست، اشیاء با مرجع مشخصی به موجودیت اضافه می شوند. چون در مثال دوم کل بسته به موجودیت اضافه می شود، ممکن است مشکلاتی بروز کند زیرا بیش از حد نیاز شیء اضافه می شود.

اگر چند شیء همنام حاصل شود دلیل آن، بخش USE است زیرا هیچ یک از اشیاء مشاهده نمی شوند و عملیات کامپایلی که از شیء استفاده می کند با شکست مواجه می شود.

در بخش اعلان موجودیت board_design سیگنالی به نام sys_clk وجود دارد. در موجودیت board_design و تمام معماری های آن می توان به این سیگنال رجوع کرد. در این مثال، board_design فقط معماری data_flow را دارد.

بنابراین سیگنال sys_clk را می توان از درون موجودیت doard_design و معماری data_flow خواند و به آن مقدار تخصیص داد.

در معماری data_flow سیگنال int_bus از نوع bus_type اعلان شده که این نوع در بسته sigdecl تعریف شده است.

بنابراین، نوع bus_type در معماری data_flow در دسترس است. چون سیگنال در بخش اعلان معماری اعلان شده است.

فقط در معماری data_flow یا دستورات پروسس درون آن قابل ارجاع است.

این آموزش بیش از ۳ سال قبل ارسال شده و اکنون در لیست بهروزرسانیهای سایت قرار دارد. اگر پیشنهاد یا انتقادی برای بهبود آموزش دارید، خوشحال میشیم به ما اطلاع بدهید.